Содержание

Введение

1. Исследовательская часть

1.1 Логические основы работы ЭВМ

1.2 Виды сумматоров

1.2.1 Четвертьсумматор

1.2.2 Полусумматор

1.2.3 Полный одноразрядный двоичный сумматор

1.3 Классификация сумматоров

1.4 Важнейшие параметры сумматоров

1.5 Характерные неисправности и пути их исправления

2. Технологическая часть

2.1 Расчёт полного одноразрядного сумматора

2.2 Выбор элементной базы

3. Расчёт надёжности

4. Охрана труда

4.1 Микроклимат рабочей зоны разработчика

4.2 Освещение рабочего места

4.2.1 Расчет естественного освещения

4.2.2 Расчет искусственного освещения

4.3 Воздействие шума на программиста

4.4 Опасность повышенного уровня напряженности электромагнитного поля

4.5 Электробезопасность, статическое электричество

4.6 Пожарная безопасность

4.7 Допуск к работе

4.8 Техника безопасности при работе с компьютером

Заключение

Список использованной литературы

Введение

Цифровая электроника — это быстро развивающаяся область современной вычислительной техники. Всю историю развития вычислительной техники принято делить на три периода — домеханический, механический, электронно-вычислительный. Эти три периода включают в себе промежуток времени от счета на пальцах до вычислений сверхмощных компьютеров. Цифровая электроника в настоящее время все более и более вытесняет традиционную аналоговую. Ведущие фирмы, производящие самую разную электронную аппаратуру, все чаще заявляют о полном переходе на цифровую технологию. Цифровая техника обрабатывает, хранит и отображает информацию, необходимую для решения самых разнообразных проблем. Все перечисленное производится с помощью электронных схем — полупроводниковых интегральных схем. Неизбежной платой за производство новой информации являются затраты энергии. От того, как организованы интегральные схемы зависит, как быстро, точно и какими энергозатратами обеспечивается производство информации. Высокие скорости и низкие энергетические затраты — это две главных цели развития элементной базы цифровой техники. Эти цели достигаются за счет совершенствования системных решений цифровых устройств, принципов и алгоритмов их функционирования. Другая группа средств достижения этих целей включает схемотехнические, структурные и топологические решения базовых логических вентилей и элементарных переключателей. Причем, это относится как к бытовой технике (аудио,- видеоаппаратура, средства связи), так и к профессиональной технике (измерительная, управляющая аппаратура). Ставшие уже привычными персональные компьютеры также полностью реализованы на основе цифровой технологии. Видимо, в ближайшем будущем полностью аналоговые устройства будут применяться только в тех редких случаях, когда требуется получить рекордные значения некоторых параметров электронных устройств (например, быстродействия). Достоинство и недостатки аналоговых и цифровых устройств

Изначально все электронные устройства были только лишь аналоговыми, но со временем, когда требования к электронным устройствам выросли, начали проявляться недостатки аналоговой электроники. Всё дело в том, что аналоговые сигналы чувствительны к всяким паразитным воздействиям — шумам, наводкам, помехам, которые искажают полезный сигнал, а при передаче сигнала на большие расстояния они ослабляются.

В отличие от аналоговых сигналов, цифровые, имеющие всего два уровня разрешённых значений, защищены от воздействия шумов, наводок и помех гораздо лучше. Имеющиеся небольшие отклонения от разрешённых значений никак не искажают цифровой сигнал, так как всегда существуют зоны допустимых отклонений. Однако у цифровых устройств имеется крупный недостаток. Дело в том, что для распознавания уровня сигнала необходимо, чтобы этот уровень поддерживался в течении определённого интервала. А аналоговый сигнал может принимать любое значение в течении любого, даже самого минимального, периода времени. Поэтому часто аналоговые сигналы называют непрерывными во времени, а цифровые — дискретные по времени сигналы. Отсюда можно сделать вывод, что максимально достижимое быстродействие аналоговых устройств всегда принципиально выше, чём цифровых.

Основной элементарной операцией, выполняемой над кодами чисел в цифровых устройствах, является арифметическое сложение.

Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учет знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в арифметическо-логических устройствах или процессорных элементах, ядром которых являются сумматоры.

В процессе выполнения данной дипломной работы будет предложен комплект конструкторской документации на устройство «Одноразрядный сумматор» на логических элементах.

Исследовательская часть

1.1 Логические основы работы ЭВМ

Во всех современных компьютерах применяется логическая система, изобретенная Джорджем Булем. Тысячи микроскопических электронных переключателей в кристалле интегральной схемы сгруппированы в системы «вентилей», выполняющих логические операции, т.е. операции с предсказуемыми результатами. На приведенных здесь рисунках показаны элементарные логические вентили И, ИЛИ и НЕ. Все остальные логические схемы компьютера могут быть построены на основе вентилей этих трех типов.

Соединенные в различные комбинации, логические вентили дают возможность компьютеру решать задачи с помощью закодированных импульсов его двоичного языка. На вход каждого логического вентиля поступают электрические сигналы высокого и низкого уровней напряжения, которые он интерпретирует в зависимости от своей функции и выдает один выходной сигнал также либо низкого, либо высокого уровня. Эти уровни соответствуют одному из состояний двоичной системы: да — нет, единица — нуль, истина — ложь. Простой вентиль И, например, выдает на выходе 1 в том и только том случае, когда на все его входы поступает 1, что соответствует логическому значению «истина».

Действуя в соответствии с определенными правилами, логические вентили координируют движение данных и выполнение инструкций в компьютере. Так, определенный элемент данных может пройти от одного блока к другому только в том случае, если на входах конкретного вентиля И оба сигнала будут равны 1.

Изображенные на рисунке 1 вентили выполняют логическую операцию И. Они показаны символическими обозначениями, принятыми в электронике. Хотя у каждого вентиля И здесь изображено по два входа, на самом деле число входов может быть и большим. Однако, как у всех логических вентилей, выход у него только один. Вентиль И по определению выдает значение 1, т. е. логическое значение «истина», в том и только том случае, когда на оба его входа поступает 1, т. е. «истина». Три верхних вентиля дают на выходе 0, или «ложь», поскольку ни у одного из них на оба входа не поступает по 1. Лишь у нижнего вентиля на выходе появляется 1, т. е. «истина».

Как и вентили И, вентили ИЛИ могут иметь больше двух входов, но только один выход. Однако к входам этих вентилей «предъявляются менее строгие требования». Как показано на рисунке 2, на выходе вентиля ИЛИ 1, или «истина», получается и в том случае, когда по крайней мере на один из его входов поступает 1. Только в одном случае вентиль ИЛИ выдает двоичный 0, или логическое значение «ложь», — когда логическое значение «ложь» поступает на все его входы.

Эти треугольники с кружочком на конце рисунка 3 — символические изображения вентиля НЕ, или инвертера. В отличие от вентилей И, ИЛИ вентиль НЕ имеет лишь один вход, значение которого он меняет на обратное, превращая 0 в 1, а 1 в 0. Вентили НЕ часто комбинируют с вентилями И и ИЛИ, в результате чего получаются вентили И-НЕ («и-не») и ИЛИ-НЕ («или-не»). Такие комбинированные схемы обрабатывают входные сигналы так же, как вентили И, ИЛИ, а затем инвертируют выходной сигнал.

1.2 Виды сумматоров

1.2.1 Четвертьсумматор

Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Наиболее известны для данной схемы названия: элемент “сумма по модулю 2” и элемент “исключающее ИЛИ”. Схема изображённая на рисунке 4 имеет два входа а и b для двух слагаемых и один выход S для суммы. Работу её отражает таблица 2 истинности, а соответствующее уравнение имеет вид:

Таблица 2 – Таблица работы четвертьсумматора

Рисунок 4 – Схема четвертьсумматора

Данный элемент выпускается в виде интегральных схем типа ЛП5 (серии 133, 155, 530, 531, 533, 555, 1531, 1533); ЛП12 (555); ЛП107 (100, 500, 1500); ЛП2 (561, 564); ЛП14 (1561) и т. п.

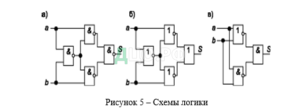

Реализуем четвертьсумматор в базисах И-НЕ, ИЛИ-НЕ и с использованием только одного инвертора, для чего преобразуем уравнение (1):

1.2.2 Полусумматор

Схема полусумматора на рисунке 6 имеет два входа a и b для двух слагаемых и два выхода: S — сумма, P — перенос. Обозначением полусумматора служат буквы HS (half sum — полусумма). Работу его отражает таблица 3 истинности, а соответствующие уравнения имеют вид:

Таблица 3 — Таблица работы полусумматора

Рисунок 6 – Схема полусумматора

Из уравнений (5) следует, что для реализации полусумматора требуется один элемент “исключающее ИЛИ” и один двухвходовый вентиль “И” рисунок 8б.

1.2.3 Полный одноразрядный двоичный сумматор

Схема полного одноразрядного сумматора изображённого на рисунке 7 имеет три входа: a, b — для двух слагаемых и p — для переноса из предыдущего (более младшего) разряда и два выхода: S — сумма, P — перенос в следующий (более старший) разряд. Обозначением полного двоичного сумматора служат буквы SM. Работу его отражает таблица 4 истинности:

Таблица 4 – Таблица работы SM

Рисунок 7 – Схема полного одноразрядного сумматора

1.3 Классификация сумматоров

В зависимости от системы счисления различают следующие сумматоры:

- двоичные;

- двоично-десятичные (в общем случае двоично-кодированные);

- десятичные;

- прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов складываемых чисел

различают следующие сумматоры:

- одноразрядные;

- многоразрядные.

По числу входов и выходов одноразрядных двоичных сумматоров различают следующие виды:

- четвертьсумматоры (элементы «сумма по модулю 2», «элементы», «исключающие ИЛИ»), характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

- полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноименные разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд);

- полные одноразрядные двоичные сумматоры, характеризующиеся наличием трех входов, на которые подаются одноименные разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд).

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

- последовательные, в которых обработка чисел ведется поочередно, разряд за разрядом на одном и том же суммирующем узле.

- параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется свой суммирующий элемент.

- параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется свой суммирующий элемент.

Параллельный сумматор в простейшем случае представляет собой n одноразрядных сумматоров, последовательно (от младших разрядов к старшим) соединённых цепями переноса. Однако такая схема сумматора характеризуется сравнительно невысоким быстродействием, так как формирование сигналов суммы и переноса в каждом i-ом разряде производится лишь после того, как поступит сигнал переноса с (1-1)-го разряда. Таким образом, быстродействие сумматора определяется временем распространения сигнала по цепи переноса. Уменьшение этого времени — основная задача при построении параллельных сумматоров.

Для уменьшения времени распространения сигнала переноса применяют конструктивные решения, когда используют в цепи переноса наиболее быстродействующие элементы; тщательно выполняют монтаж без длинных проводников и паразитных ёмкостных составляющих нагрузки и (наиболее часто) структурные методы ускорения прохождения сигнала переноса.

По способу организации межразрядных переносов параллельные сумматоры, реализующие структурные методы, делят на сумматоры:

- с последовательным переносом;

- с параллельным переносом;

- с групповой структурой;

- со специальной организацией цепей переноса.

Среди сумматоров со специальной организацией цепей переноса можно указать:

- сумматоры со сквозным переносом, в которых между входом и выходом переноса одноразрядного сумматора оказывается наименьшее число логических уровней;

- сумматоры с двухпроводной передачей сигналов переноса;

- сумматоры с условным переносом (вариант сумматора с групповой структурой, позволяющий уменьшить время суммирования в 2 раза при увеличении оборудования в 1,5 раза);

- асинхронные сумматоры, вырабатывающие признак завершения операции суммирования, при этом среднее время суммирования уменьшается, поскольку оно существенно меньше максимального.

Сумматоры, которые имеют постоянное время, отводимое для суммирования, независимое от значений слагаемых, называют синхронными.

По способу выполнения операции сложения и возможности сохранения результата сложения можно выделить три основных вида сумматоров:

- комбинационный, выполняющий микрооперацию «S = А плюс В», в котором результат выдаётся по мере его образования (это комбинационная схема в общепринятом смысле слова);

- сумматор с сохранением результата «S = А плюс В»;

- накапливающий, выполняющий микрооперацию «S = S плюс В».

Последние две структуры строятся либо на счётных триггерах (сейчас практически не используются), либо по структуре «комбинационный сумматор — регистр хранения» (сейчас наиболее употребляемая схема).